AMDK11

Użytkownik-

Postów

141 -

Dołączył

-

Ostatnia wizyta

Ostatnie wizyty

Blok z ostatnimi odwiedzającymi dany profil jest wyłączony i nie jest wyświetlany użytkownikom.

Osiągnięcia AMDK11

Bywalec (3/5)

63

Reputacja

-

Przez kilka stron na forum Anandtech pisali o tym, ale ktoś wrzucił to: ‘novalake’ Intel Nova Lake CPU with 64-bit extensions, MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, CX16, AES, PREFETCHW, PCLMUL, RDRND, XSAVE, XSAVEC, XSAVES, XSAVEOPT, FSGSBASE, PTWRITE, RDPID, SGX, GFNI-SSE, CLWB, MOVDIRI, MOVDIR64B, WAITPKG, ADCX, AVX, AVX2, BMI, BMI2, F16C, FMA, LZCNT, PCONFIG, PKU, VAES, VPCLMULQDQ, SERIALIZE, HRESET, AVX-VNNI, UINTR, AVXIFMA, AVXVNNIINT8, AVXNECONVERT, CMPCCXADD, AVXVNNIINT16, SHA512, SM3, SM4, PREFETCHI, APX_F, AVX10.1, AVX10.2 and MOVRS instruction set support. ‘znver6’ AMD Family 1ah core based CPUs with x86-64 instruction set support. (This supersets BMI, BMI2, CLWB, F16C, FMA, FSGSBASE, AVX, AVX2, ADCX, RDSEED, MWAITX, SHA, CLZERO, AES, PCLMUL, CX16, MOVBE, MMX, SSE, SSE2, SSE3, SSE4A, SSSE3, SSE4.1, SSE4.2, ABM, XSAVEC, XSAVES, CLFLUSHOPT, POPCNT, RDPID, WBNOINVD, PKU, VPCLMULQDQ, VAES, AVX512F, AVX512DQ, AVX512IFMA, AVX512CD, AVX512BW, AVX512VL, AVX512BF16, AVX512VBMI, AVX512VBMI2, AVX512VNNI, AVX512BITALG, AVX512VPOPCNTDQ, GFNI, AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, PREFETCHI, AVXVNNIINT8, AVXIFMA, AVX512FP16, AVXNECONVERT, AVX512BMM and 64-bit instruction set extensions.) Prawdopodobnie w NowaLake będzie ale nie wiem czy w Zen6. Z drugiej strony i tak minie trochę czasu zanim APX się upowrzechni. EDIT: FRED jest w PantherLake i jest potwierdzone że będzie w Zen6. https://www-phoronix-com.translate.goog/review/intel-fred-panther-lake?_x_tr_sl=en&_x_tr_tl=pl&_x_tr_hl=pl&_x_tr_pto=sc

-

ISA dla Zen6 jest już zamknięty i ma zawierać: APX - daje więcej „oddechu” dla kodu całkowitoliczbowego: podwaja liczbę rejestrów ogólnego przeznaczenia z 16 do 32, dodaje nowy prefix REX2 i zmiany, które mają zmniejszać liczbę loadów/storów oraz przełożeń rejestrów. To zwykle najbardziej pomaga kodowi z dużym naciskiem na integer, kompilatorom i ogólnie gęstym pętlom. AVX10 - oznacza bardziej jednolity wektorowy ISA dla x86, z możliwością konfiguracji 256-bit albo 512-bit w zależności od platformy, co ułatwia przenośność binarek i pracę kompilatorom. FRED - oznacza nowy model wejścia/wyjścia z wyjątków i przerwań, który ma zastępować stare ścieżki przez IDT i IRET krótszymi przejściami o niższej latencji i lepszej odporności systemowej. To jest przede wszystkim temat dla kernela, hypervisora i warstwy niskopoziomowej.

-

Jak przesiadka z GraniteRidge na ArrowLake?

-

Zastanawiam się, czy AMD w przypadku Zen6 zrobiło coś, aby lepiej wykorzystać dekodery 2x4-Wide w ST. Edit: Działanie front-Endu Zen5 nie jest dla mnie do końca jasne. AMD używa sprytnej gry słów, aby unikać odpowiedzi. Z jednej strony, klastry pobierania i dekodowania (2x 4-Wide) służą do zapobiegania blokowaniu wątków SMT. Oznacza to, że po wyłączeniu SMT, ST ma dostępny tylko jeden klaster, ponieważ głównym źródłem instrukcji jest 12-Wide op cache. Z drugiej strony ChatGPT twierdzi, że nie chodzi o to, że oba klastry nie są dostępne dla ST, ale o to, że w zależności od ILP i zależności w kodzie, ST wykorzystuje drugi klaster w ograniczonym zakresie. Cholera, nie ma jasnej odpowiedzi.

-

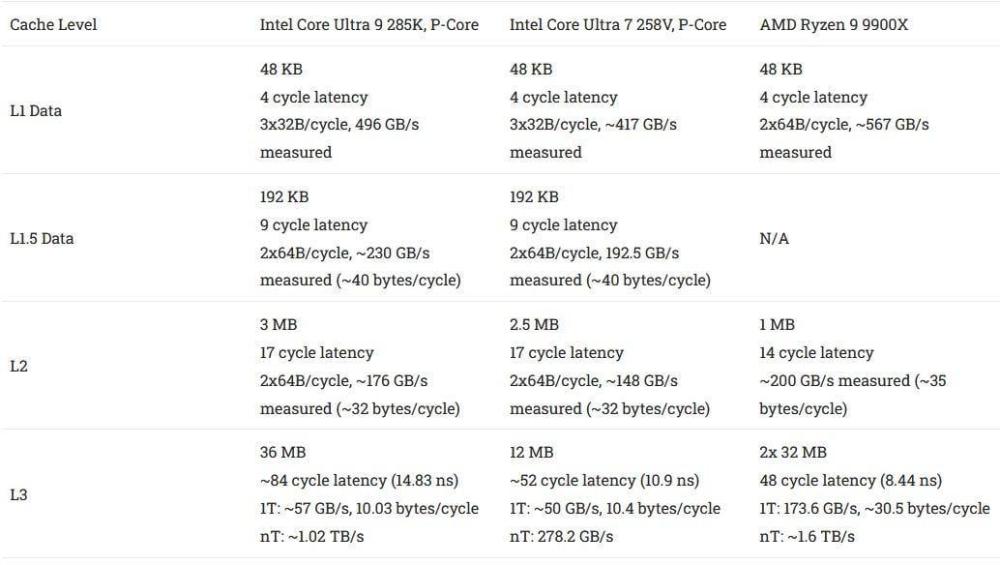

Zen5 ma problemy z przepustowością i opóźnieniami ze względu na m.in dwukrotnie szerszy front-end (w tym dekoder 2x4-Wide (łącznie 8-Wide) w porównaniu z 4-Wide (Zen4)). Zen5 pobiera teraz dwukrotnie więcej danych z L1-I, mając taką samą pojemność jak Zen4 (32 KB). ITLB L1 ma te same 64 wpisy, podczas gdy dla L2(1MB), ITLB wzrósł z 512 wpisów (Zen4) do 2048 wpisów w Zen5, czyli czterokrotnie więcej. Wszystko jest w porządku, dopóki segmenty kodu mieszczą się w 32 KB L1-I. Jednak w przypadku, gdy się nie mieszczą, Zen5 ma problemy, ponieważ opóźnienie znacznie rośnie, a przepustowość spada, mimo że L2 ITLB działa jak Victim, tj. rozszerzenie L1 ITLB. EDIT: Dla porównania: LionCove ma 64 KB L1-I i ITLB z 256 wpisami (Zen5 – ITLB 64 wpisy), podczas gdy L2 ITLB jest taki sam jak w Zen5 (2048 wpisów). W związku z tym uważa się, że w Zen6 zwiększenie L1-I do 48–64 KB i ITLB do 128–256 wpisów, wraz z innymi zmianami mikroarchitektury, powinny przynieść wymierne korzyści IPC. Powinno to pozwolić na utrzymanie wysokiej przepustowości rdzenia w większej części kodu. TLB (Translation Lookaside Buffer) w rdzeniach to bardzo szybki bufor, który trzyma kopie tłumaczeń adresów wirtualnych na fizyczne razem z bitami uprawnień i ważności z tablic stron. Rdzeń sprawdza TLB przy każdym dostępie do pamięci opartym o adres wirtualny; jeśli translacji tam nie ma, używany jest page table walker.

-

Pytanie brzmi, czy uzyskane wyniki są faktycznie przy częstotliwości około 2,0 GHz. Międzynarodowe fora są zaskoczone, że L1-I nadal jest 32 KB, ponieważ wiadomo, że Zen6 mógł m.in zmienić L1-I na 64 KB, co pomogłoby nie tylko w ST. Chyba że GB6.6.0 nie jest w stanie prawidłowo wskazać parametrów Zen6, w takim przypadku taktowanie również mogłoby nie być prawidłowe.

-

Powiedziałbym, że jest to bardzo odkrywcze i niektórzy dostaną Blue screena ze zdziwienia 😅

-

[GB6 CPU] Unknown CPU CPU: AMD Eng Sample: 100-000001713-21_N (10C 20T) Min/Max/Avg: 2083/2134/2114 MHz CPUID: B80F00 (AuthenticAMD) Single: 2268 Multi: 12866 https://t.co/Vna7WkyZG3

-

Naprawdę jest na co czekać

-

Popełniłem aktualizację BIOS UEFI(ASUS GAMING TUF B650-E WiFi): Z Version 3602 17.24 MB 2025/12/01 SHA-256 :FB926B3741EBA1E910EC533F99373160443FDDEC2C4FE2C8062E2F2292DD5BBB "1.AGESA updated to ComboAM5 PI 1.2.7.0. 2.Improves compatibility with various CPUs and devices. Note: This BIOS version cannot be rolled back to previous versions. Na Version 3827 17.23 MB 2026/02/13 SHA-256 :E63F3BBE4729B044C748358DE25984B877C14352F32F1FC4D94FE6CDB813D3C9 "1. AGESA updated to ComboAM5 PI_Pre1.3.0.0 for better security. 2. Enhanced system performance and stability. 3. Improved memory compatibility for JEDEC-compliant modules. I muszę przyznać, że podczas pierwszego trenowania pamięci RAM poszło szybko i sprawnie, a po zmianie z bezpiecznego 4800MT na (fabryczne dla kontrolera RAM w GraniteRidge) 5600MT nie było żadnych problemów. 🙂

-

Właśnie testowałem BF6 na R5 9600X, RAM 32GB i RTX5070, i zero(0) dropów 😀

-

Ponieważ predyktor Intela wymaga połączenia kablowego ze specjalną czapeczką na głowie. W przeciwnym razie BPU nie będzie działać.

-

@Phoenix. Nie przypominam sobie, aby C&C przeprowadzał taki pomiar. Myślę, że przepustowość pozostaje podobna (kilka cykli więcej), ale jest znacznie więcej pamięci L3-X3D, co oznacza dużo mniejszą potrzebę odwołań do znacznie wolniejszej pamięci RAM.

-

-

Ja również planuję aktualizację, ale tym razem do Zen6. Ciekawe, czy problem z 32 MB UEFI zostanie rozwiązany tak samo, jak brak pamięci BIOS na AM4(16MB). Widziałem już płyty główne z 64 MB UEFI i deklarowanym wsparciem Zen6. Mnie bootuje szybko, mimo że, zmieniłem obcje bootowania z tej najszybszej na pełniejszą.