AMDK11

Użytkownik-

Postów

133 -

Dołączył

-

Ostatnia wizyta

Treść opublikowana przez AMDK11

-

Naprawdę jest na co czekać

-

Popełniłem aktualizację BIOS UEFI(ASUS GAMING TUF B650-E WiFi): Z Version 3602 17.24 MB 2025/12/01 SHA-256 :FB926B3741EBA1E910EC533F99373160443FDDEC2C4FE2C8062E2F2292DD5BBB "1.AGESA updated to ComboAM5 PI 1.2.7.0. 2.Improves compatibility with various CPUs and devices. Note: This BIOS version cannot be rolled back to previous versions. Na Version 3827 17.23 MB 2026/02/13 SHA-256 :E63F3BBE4729B044C748358DE25984B877C14352F32F1FC4D94FE6CDB813D3C9 "1. AGESA updated to ComboAM5 PI_Pre1.3.0.0 for better security. 2. Enhanced system performance and stability. 3. Improved memory compatibility for JEDEC-compliant modules. I muszę przyznać, że podczas pierwszego trenowania pamięci RAM poszło szybko i sprawnie, a po zmianie z bezpiecznego 4800MT na (fabryczne dla kontrolera RAM w GraniteRidge) 5600MT nie było żadnych problemów. 🙂

-

Właśnie testowałem BF6 na R5 9600X, RAM 32GB i RTX5070, i zero(0) dropów 😀

-

Ponieważ predyktor Intela wymaga połączenia kablowego ze specjalną czapeczką na głowie. W przeciwnym razie BPU nie będzie działać.

-

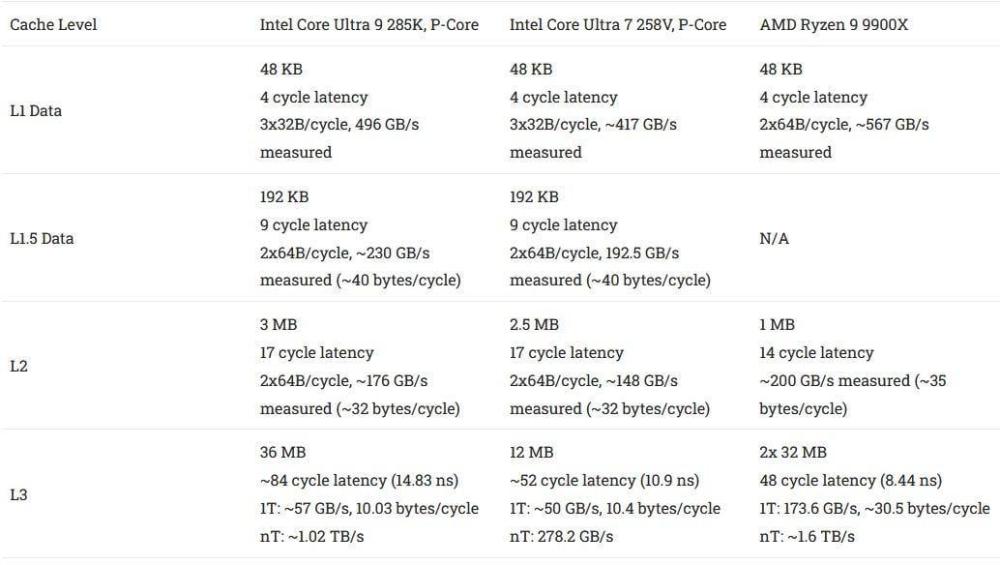

@Phoenix. Nie przypominam sobie, aby C&C przeprowadzał taki pomiar. Myślę, że przepustowość pozostaje podobna (kilka cykli więcej), ale jest znacznie więcej pamięci L3-X3D, co oznacza dużo mniejszą potrzebę odwołań do znacznie wolniejszej pamięci RAM.

-

-

Ja również planuję aktualizację, ale tym razem do Zen6. Ciekawe, czy problem z 32 MB UEFI zostanie rozwiązany tak samo, jak brak pamięci BIOS na AM4(16MB). Widziałem już płyty główne z 64 MB UEFI i deklarowanym wsparciem Zen6. Mnie bootuje szybko, mimo że, zmieniłem obcje bootowania z tej najszybszej na pełniejszą.

-

Ostatnim komputerem stacjonarnym z procesorem Intel, jaki miałem, był i7 5820K. Nie mam odniesienia do 14 generacji Intela. Zazwyczaj pierwszy, wstępny(automatyczny) proces kalibracji pamięci RAM na Ryzen 9000 jest dość długi (czasami trzeba restartować komputer). Myślę że to kwestia stopnia kompatybilności RAM DDR5 z płytą główną(brak oficjalnego wsparcia modułów na liście BIOS UEFI). Ale po jego zakończeniu i samodzielnym ustawieniu reszty w BIOS-ie (mój ASUS z automatu utawia RAM na bezpieczne 4800MT, podczas gdy kontroler Zen5 ma nominalnie 5600MT), jest stabilnie jak skała, a system Windows 11 Pro ładuje się błyskawicznie z dysku NVMe.

-

Zastanawiałem się nad problemem dropów FPS na Zen5 (nie korzystałem z poprzednich generacji Zen, więc nie mam na ich temat zdania). Mam sugestię na nowy wątek: "Brak dropów FPS na Ryzen 9000! Co powinienem zrobić, które ustawienia zmienić, ewentualnie co zdup**yć, żeby spowodować dropy FPS? Pilnie proszę o pomoc!"

-

@j4z Podobno masz dropy na 9800X3D. To prawda?

-

@MarcoSimone Aż sprawdzę z ciekawości BF6. Jedynie gdzie nie mam takiej płynności(GPU) to na demo Gothic Remake. Przy wyłączonym m.in RT dalej był nisk FPS. Zluzowałem suwaki przy pewnych ustawieniach i jest około 70-80 FPS, ale dropów nieuświadczyłem.

-

Jak tylko będę miał okazję, kupię tą grę i sprawdzę Edycja: w celu uzupełnienia mojego konfigu, płyta główna i RTX 5070 pochodzą od ASUS-a. Zasilacz to Corsair ATX3.1 1000W, a oba złącza zasilania procesora są podłączone. Ostatnio grałem w Crysis Remaster 1 (ukończyłem), a teraz w Crysis Remaster 2. Szybkie ładowanie poziomów i 100% stabilności + wysoki FPS podczas gry na mapie, niezależnie od chaosu panującego na ekranie.

-

Na jakich ustawieniach procesora? Po OC, UV czy na defultowych? Ja mam 9600X na dwfult(80W) czyli nastawy fabryczne. Zero OC. Przy obniżonych napięciach(UV) względem fabrycznych w pewnych sytuacjach/scenariuszach też może być za małe napięcie(wcale bym się nie zdziwił).

-

Ach, te dropy, których nie doświadczam na moim R5 9600X(80W) + 32 GB (2 x 16 GB) RAM 5600MT + RTX 5070 + 2 TB NVMe PCI-Ex 4.0 (prędkość 6000-7000 MB/s, chłodzonym radiatorem z rurkami cieplnymi i wentylatorem) z jakiegoś dziwnego powodu Nie wiem. Może te dropy są od podkręcania lub UV? Mam ustawienia fabryczne i żadnych spadków, gram i testuję różne gry. Zawsze wysoki FPS w rozdzielczości 2560x1440 i, o dziwo, żadnych spadków. Jedyny raz, kiedy ich doświadczyłem, to w Train Driver 2, gdzie częśći mapy ładują się okresowo, a jednocześnie wcześniej przejechane są usuwane. Ale to tam normalne. Na przykład w MaSzynie 26 stycznia nie ma spadków na maksymalnych ustawieniach. To samo w ETS2. Mam dość dużą bibliotekę gier na Steamie.

-

NVL 8+16 Die TSMC N2 ~110+mm2 NVL 8+16 bLLC Die TSMC N2 ~150+mm2 Zen2 CCD: 2*4 Core 2*16 MB L3 TSMC N7 ~77 mm2 Zen3 CCD: 8 Core 32MB L3 TSMC N7 ~83 mm2 Zen4 CCD : 8 Core 32MB L3 TSMC N5 ~72 mm2 Zen5 CCD : 8 Core 32MB L3 TSMC N4 ~71 mm2 Zen6 CCD : 12 Core 48MB L3 TSMC N2 ~76 mm2(50% więcej dla rdzeni + około 30-40% miejsca poszło na rozbudowę logiki rdzeni(IPC)).

-

Zaprzestałem podkręcania po zakończeniu przygody z LGA2011v3 i procesorem i7 5820K. Z czasem tracił stabilność, mimo że osiągał maksymalną temperaturę 75-78°C pod obciążeniem benchmarkowym na Noctua NH-D15s z trzema wentylatorami. Wtedy jeszcze dało się ugrać 500-800+ MHz. Teraz dążenie do 5% jest moim zdaniem bezcelowe, ponieważ obniża żywotność systemu, a jednocześnie powoduje nieproporcjonalnie wysoki pobór mocy i wysokie temperatury w strukturze krzemu. Wystarczy że zostanie uruchomiony AVX512, a niestabilność, zawieszanie się lub restarty są możliwe. Teraz skupiam się na absolutnej stabilności i żywotności. R5 9600X i tak jest kilka razy szybszy niż 5820K, a moja(dawna) psychologiczna bariera 4 GHz została już dawno przekroczona 😉

-

Też w to wątpię. Wysoki wynik SC(SMT) został już wyjaśniony. Powyższy wynik to błąd testu CB podczas przełączania wątków/rdzeni na RaptorLake-S. Edit: Zen2 CCD: 2*4 Core 2*16 MB L3 TSMC N7 ~77 mm2 Zen3 CCD: 8 Core 32MB L3 TSMC N7 ~83 mm2 Zen4 CCD : 8 Core 32MB L3 TSMC N5 ~72 mm2 Zen5 CCD : 8 Core 32MB L3 TSMC N4 ~71 mm2 Zen6 CCD : 12 Core 48MB L3 TSMC N2 ~76 mm2

-

Podobno może być to wynik QS/ES Zen6. https://forums-anandtech-com.translate.goog/threads/cinebench-2026.2633409/page-5?_x_tr_sl=en&_x_tr_tl=pl&_x_tr_hl=pl&_x_tr_pto=sc Zen5(R5 9600X) + DDR5 2x16GB 5600MT ~5.4GHz ST 525p SC(SMT) 719p Oczywiście wyższe modele Zen5 np R9 9950X mają wyższe taktowanie ST/SC ~5.7GHz(+5.5%). ?Zen6 QS/ES? SC(SMT) 1072p(+49%!!!) Na forum AnandTech dla ST obliczają ~800p(+52%), jeśli zachować proporcje ST do SC(SMT) Zen5. Edit: Jeśli to nie NovaLake z SMT(HT) i jeśli to nie Zen5 na ciekłym azocie, a faktycznie QS/ES Zen6 to wynik jest niesamowity. Mike Clark(Szczególnie ostatnie zdanie):

-

Ma to do tego, że AMD nazywa współbieżną wielowątkowość skrótem używanym w branży od momentu powstania koncepcji SMT. To właśnie Intel wymyślił swoją marketingową nazwę na swoją implementację SMT. I to, że Intel wcale nie był pierwszy.

-

AMD po prostu nie nadało swojej implementacji SMT własnej nazwy marketingowej. Więc czy to Intel HHT, czy AMD SMT, oba są implementacjami SMT (Simultaneous Multithreading). Pamiętam, że w czasach Athlona 64 panowało zamieszanie, ponieważ Intel miał Hyper Threading, a AMD Hyper Transport (linie komunikacyjne między rdzeniami i z chipsetem) i niektórzy uważali, że obie technologie to to samo.

-

Chyba że będą to wątki a nie ilość rdzeni XD

-

@Kyle HT to Intelowska, marketingowa nazwa SMT.

-

Zobaczysz że HT wróci. LionCove to nowa baza i całkowicie inne podejście dla Intela więc nie ryzykował wdrażania HT za pierwszym podejściem. Lip Bu Tan powiedział jasno że odejście od HT(SMT) było błędem i zamierza przywrócić.

.thumb.png.7e1041683cee8abba8248da24394d845.png)

.thumb.png.63569957ad354bc4ac4d592baeea795b.png)